# Aceleración del cambio de propietario de un cerrojo en multiprocesadores DSM

Esther Rodríguez, Benjamín Sahelices, Diego R. Llanos, Pablo Ibáñez, Víctor Viñals\*\* y José M. Llabería\*\*\*

#### Resumen

El método más común para acceder a variables compartidas en aplicaciones paralelas es el uso de secciones críticas implementadas mediante cerrojos. En este artículo nos centraremos en el cambio de propietario de un cerrojo en multiprocesadores DSM cuyos controladores de coherencia serializan los accesos a una variable usando NACKS. Proponemos un mecanismo, basado en el marcado de bloques de cerrojo, que reduce el tráfico de coherencia en situaciones de contención. Los resultados experimentales muestran una mejora de hasta un 9,8 % en la ejecución de la fase paralela de aplicaciones pertenecientes a Splash-2.

#### 1. Introducción

El método más común para acceder a variables compartidas en aplicaciones paralelas es el uso de secciones críticas implementadas mediante cerrojos. El uso concurrente de un cerrojo genera múltiples solicitudes simultáneas sobre un mismo controlador, lo que puede dar lugar a situaciones de contención. Para serializar las solicitudes a una variable, los controladores de coherencia pueden, o bien rechazar solicitudes (NACK), o bien almacenar dichas solicitudes en buffers. En ambos tipos de controladores, las situaciones de contención se asocian a incrementos puntuales de mensajes de

coherencia. Este tráfico incrementa el tiempo de cambio de mano de una sección crítica lo cual reduce los beneficios de la programación paralela.

El elevado tráfico de mensajes provocado por la contención sobre un cerrojo puede verse aliviado con el uso de algoritmos exponenciales de back-off [10]. Esta técnica tiene el inconveniente de que su ajuste es muy dependiente de la aplicación y de la arquitectura. Otra forma de atenuar la contención es el uso de colas hardware [4, 5, 7, 11]. Esta técnica mejora la transferencia de propiedad del cerrojo y reduce el ancho de banda necesario, aunque requiere modificaciones hardware y del protocolo de coherencia.

Cuando la serialización de los mensajes de coherencia a un bloque se hace mediante buffer, la técnica de combinación de solicitudes de lecturas pendientes [1] mejora la adquisición del cerrojo en aplicaciones con alta contención, agrupando peticiones de lectura pendiente y gestionándolas en una sola operación. Por su parte, la técnica del Cortocircuito [3] cambia el orden en el que el controlador de coherencia selecciona la solicitud que va a ser procesada, acelerando el cambio de propietario del cerrojo.

Existen también situaciones de alta contención cuando diferentes nodos acceden a diferentes datos, los cuáles están protegidos por el mismo cerrojo. Un posible enfoque para deshacer estas situaciones de contención es la ejecución de cerrojos como transacciones especulativas [2, 8]. En este tipo de transacciones se permite a varios nodos leer y escribir concurrentemente de forma especulativa sobre datos compartidos. Cuando se detecta un error

<sup>\*</sup>Departamento de Informática, Universidad de Valladolid, {mesther,benja,diego}@infor.uva.es.

<sup>\*\*</sup>Departamento de Informática e Ingeniería de Sistemas, Universidad de Zaragoza, {imarin,victor}@unizar.es

<sup>\*\*\*</sup>Departamento de Arquitectura de Computadores, Universidad Politécnica de Cataluña, llaberia@ac.upc.edu

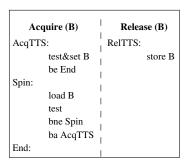

Figura 1: Código de adquisición y liberación del cerrojo

de especulación hay que disponer de un mecanismo de recuperación.

En este artículo nos centraremos en el cambio de propietario de un cerrojo en multiprocesadores DSM cuyos controladores de coherencia serializan los accesos a una variable usando NACKS. Proponemos un mecanismo, basado en el marcado de bloques de cerrojo, que reduce el tráfico de coherencia en situaciones de contención. Los resultados experimentales muestran una mejora de hasta un 9,8 % en la ejecución de la fase paralela de aplicaciones pertenecientes a Splash-2 [12].

El resto del artículo se estructura como sigue. En la sección 2 describimos un ejemplo de cambio de propietario de un cerrojo en una sección crítica con alta contención. En la sección 3 analizamos el mismo ejemplo bajo la técnica de marcado propuesta. En la sección 4 presentamos los resultados de simulación usando aplicaciones pertenecientes a Splash-2 y en la sección 5 mostramos las conclusiones.

### Cambio de propietario del cerrojo

En esta sección describimos el modelo de coherencia base, presentando un ejemplo que refleja la transferencia del cerrojo entre diferentes procesadores.

### 2.1. Modelo de coherencia base

El modelo base con el que trabajaremos está basado en un multiprocesador CC-NUMA

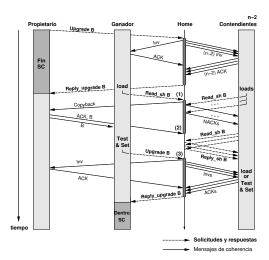

Figura 2: Ejemplo de cambio de propietario del cerrojo con el sistema base

con un protocolo de coherencia cache del tipo MESI similar al del sistema SGI Origin-2000 [6]. Las peticiones son de tres tipos: READ\_SH, READ\_OWN y UPGRADE. El controlador responde con REPLY\_SH, REPLY\_EXCL y REPLY\_UPGR, respectivamente. Además, la invalidación de copias de un bloque se realiza mediante mensajes INV y las solicitudes de transferencia cache-cache se realizan mediante mensajes COPYBACK.

El controlador de coherencia marca un bloque en estado "ocupado" cuando recibe una solicitud sobre dicho bloque que requiere la intervención de un tercer nodo. Cualquier solicitud posterior sobre dicho bloque se responde con un reconocimiento negativo (NACK). Una vez que la solicitud inicial ha finalizado, el bloque pasa a estar disponible para nuevas solicitudes.

## 2.2. Ejemplo de cambio de propietario del cerrojo

En la Figura 1 se muestra el código de adquisición y liberación de la variable cerrojo. La adquisición se realiza mediante una primitiva  $Test \mathcal{B}(TaS)$  con la única variante de que primero se realiza el TaS. La liberación del cerrojo se hace mediante una instrucción de almacenamiento.

En la figura 2 se muestra un ejemplo de cambio de propietario de una seccón crítica protegida por un cerrojo almacenado en un bloque B. Llamaremos "propietario" al nodo que está dentro de la sección crítica; "contendientes" serán los n-1 nodos que intentan adquirirla; "ganador" es aquel nodo contendiente cuyo READ\_SH es el primero en tratarse tras la apertura del cerrojo. Finalmente, "home" es aquel nodo cuyo controlador de coherencia gestiona las solicitudes de acceso al bloque B. El ejemplo comienza cuando el propietario sale de la sección crítica enviando upgrade, mientras los contendientes realizan espera activa local. El ejemplo continúa como sigue:

- Cuando el home recibe la solicitud UP-GRADE, invalida las copias del bloque y cambia su estado a "ocupado". Una vez recibidas todas las respuestas a las invalidaciones, envía REPLY\_UPGR al propietario, dejando el bloque en estado "no ocupado".

- Los n-1 contendientes sufren un fallo de cache de la variable B y envían una solicitud READ SH al home.

- El primer READ\_SH que llegue al home será el del nodo ganador (ver (1) en la Figura 2). El home atiende esta solicitud mandando un COPYBACK al propietario y cambiando el bloque a estado "ocupado". Al resto de solicitudes se responderá con NACK.

- El propietario responde al home (ACK, B, ver (2) en la Figura 2) y al nodo ganador (REPLY\_SH). El bloque pasa a estar "no ocupado".

- En este punto las solicitudes de los contendientes serán atendidas generandose múltiples copias del bloque B. Todos ellos verán la sección crítica abierta.

- El ganador ejecuta la instrucción TaS y envía un upgrade al Home.

- El home procesa el UPGRADE del ganador (ver (3) en la Figura 2), enviando solicitudes de invalidación (INV) y cambiando el estado del bloque a "ocupado".

El home espera la llegada de todas las respuestas de invalidación (ACK), cambia el estado del bloque a "no ocupado" y envía un REPLY\_UPGR al ganador. El cambio de propietario ha sido realizado y el ganador puede ejecutar la sección crítica.

Los contendientes que recibieron el bloque abierto (ver intervalo entre (2) y (3) en la Figura 2), enviarán posteriormente solicitudes upgrade debido a la operación TaS. Cada una de estas solicitudes UPGRADE generará una transacción cache-cache debido a que el bloque estará en estado exclusivo. La serialización en la ejecución de estas solicitudes UPGRADE puede provocar que, cuando la solicitud de liberación de la sección crítica llegue al home, éste todavía siga procesando alguna de ellas. La solicitud de liberación será rechazada (NACK) retrasando el cambio de mano de la sección crítica y por lo tanto el tiempo de ejecución de la aplicación. La técnica del marcado tiene como objetivo reducir al mínimo el número de copias del bloque B cuando la sección crítica ha sido liberada y antes de que vuelva a ser adquirida, con el objetivo de reducir el número de TaS realizados por nodos contendientes perdedores.

### 3. Técnica del marcado

La técnica del marcado de bloques se basa en identificar los puntos (2) y (3) de la Figura 2 y evitar la proliferación de copias del bloque B antes de que sea adquirido, debido a que estas copias son inútiles y no contribuyen al avance del sistema. Para conseguirlo el propietario marca el bloque B (que pasaremos a llamar B') en el instante en el que se genera el mensaje UPGRADE de liberación de la sección crítica. En el momento en el que el home reciba el UPGRADE almacenará esta marca. La primera solicitud read sh posterior que el home reciba (nodo ganador) se atiende normalmente. El resto de solicitudes READ SH sobre el bloque marcado serán rechazadas, evitando así que en este instante prolifere el número de copias del bloque B', ya que en este momento el cerrojo está abierto. Finalmente, se recibe una solicitud UPGRADE generada por el nodo ganador

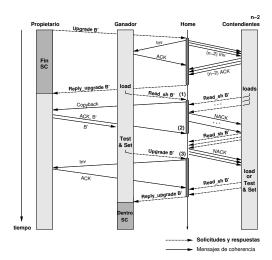

Figura 3: Ejemplo de cambio de propietario del cerrojo con la técnica del marcado

al ejecutar una instrucción TaS. El cambio de mano se considera consumado y el protocolo vuelve a su funcionamiento habitual.

A continuación aplicaremos la técnica de marcado sobre el escenario propuesto en la sección anterior. Seguidamente describiremos una posible implementación. Para concluir, presentaremos una variante a la técnica.

### 3.1. Ejemplo de cambio de propietario del cerrojo

En la Figura 3 representamos el mismo ejemplo de la Figura 2 pero aplicando nuestra técnica. Cuando se recibe la solicitud marcada de liberación de la sección crítica (UP-GRADE B'), el controlador de coherencia interpreta que dicha sección crítica está abierta. El primer READ SH que se recibe después de la solicitud marcada, se interpreta como un intento de entrada en la sección crítica y se le da prioridad. Con este fin se rechazan el resto de solicitudes READ SH que llegan de los contendientes (ver intervalo (2)-(3) de la Figura 3). La posterior recepción de la solicitud de UPGRADE indica la entrada en la sección crítica, por lo que el controlador vuelve a su comportamiento estándar.

Cuando los contendientes consiguen la copia

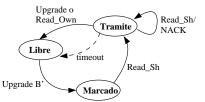

Figura 4: Diagrama de transición de estados para el bloque del cerrojo

del bloque, el nodo ganador ya está dentro de la sección citica por lo que ven dicha sección "cerrada". Así, en vez de enviar una solicitud TaS, se mantienen haciendo espera activa en su copia local. Esto no se muestra en la figura.

### 3.2. Implementación de nuestra técnica en el controlador de coherencia

A partir del ejemplo anterior, identificamos tres estados para el bloque del cerrojo (ver Figura 4): libre, marcado y trámite. El estado marcado se asocia a la recepción de la solicitud marcada de liberación de la sección crítica. El estado trámite se asocia a la recepción de una solicitud READ\_SH posterior a la solicitud (marcada) de liberación de la sección crítica. El estado libre se asocia al comportamiento estándar del protocolo.

Las transiciones entre los estados ocurren de la siguiente manera. Al estado marcado se llega tras la recepción del upgrade marcado. La posterior recepción de la primera solicitud READ\_SH provoca la transición al estado trámite. Durante el estado trámite se rechazan todas las solicitudes READ\_SH que le lleguen. La posterior recepción de la primera solicitud de escritura hace que el estado cambie a libre. A partir de este instante el protocolo se comporta como se ha descrito en el sistema base.

En cada controlador de coherencia se implementa una tabla de marcado en donde se almacenan aquellos bloques marcados junto con su estado. Hay una tabla de marcado por cada controlador. El número de entradas de la tabla deberá corresponderse con el número máximo de secciones críticas que simultáneamente gestionará cada controlador. Se ha comprobado experimentalmente que una entrada es

suficiente para las aplicaciones consideradas.

### 3.2.1. Garantía de progreso del nodo ganador

Nuestra técnica es vulnerable a situaciones de falsa compartición o a la muerte de un hilo. En el caso de la falsa compartición, puede ocurrir que el primer READ SH que se reciba cuando la sección crítica se encuentre abierta sea el de un nodo que pretenda leer un dato almacenado en el mismo bloque en el que se encuentra el cerrojo. Si ese bloque se encontrara en estado marcado, esta solicitud provocaría una transición a estado trámite. Debido a que el nodo solicitante no pretende entrar en la sección crítica, nunca enviaría una solicitud de escritura y por lo tanto no se saldría de dicho estado. El sistema rechazaría indefinidamente cualquier solicitud sobre dicho bloque. En el caso de que un hilo interrumpa su ejecución, puede ocurrir que el bloque estuviera en estado trámite y nunca se llegara a recibir la solicitud de escritura. El resultado sería el mismo que en el caso anterior.

Para garantizar el progreso, se ha limitado el tiempo máximo de permanencia en estado trámite. En el caso de que este tiempo se supere, se volverá al estado libre. En situaciones puntuales de elevada contención, la gestión de solicitudes de coherencia se puede retrasar, haciendo que se dispare el temporizador. En esta situación el protocolo volvería a comportarse como se ha descrito en el sistema base. Los experimentos muestran buenos resultados con una ventana temporal de 3000 ciclos. Este valor está relacionado con las latencias de comunicación de la red.

### 3.3. Variante de nuestra técnica

Además de la técnica descrita, hemos considerado una variante denominada Marcado Exclusivo (MarcadoX). La técnica de Marcado Exclusivo proporciona una copia exclusiva del bloque al primer READ\_SH que llegue cuando la sección crítica esté abierta. La implementación de esta técnica requiere sólo dos estados: libre y marcado. Al estado marcado se llega tras la recepción de la solicitud (marcada)

de liberación de la sección crítica. El primer READ SH recibido a continuación corresponderá a un nodo que intenta entrar en la sección crítica. Esta solicitud dispara el cambio a estado libre. Para acelerar el cambio de propietario, este READ SH se responderá con una copia en estado exclusivo, en lugar de la copia SHARED que le correspondería. Cuando el nodo solicitante reciba la copia en exclusiva, verá la sección crítica abierta y ejecutará inmediatamente una instrucción TaS. Esta instrucción tiene muchas posibilidades de encontrar el bloque en estado modificado en la caché local, permitiendo que el nodo solicitante entre en la sección crítica sin necesidad de operaciones de coherencia adicionales.

| Processor        |                                     |

|------------------|-------------------------------------|

| Speed            | 1 Ghz                               |

| ROB/LSQ          | 64-entry, 32-entry ld/st queue      |

| Issue            | out-of-order issue/com. 4 ops/cy.   |

| Branch pred.     | 512-entry branch pred buf           |

| Cache            |                                     |

| L1 instr. cache  | Perfect                             |

| L1 data cache    | 32-Kbyte, 4-way assoc., WB,         |

|                  | 2 ports, 1-cy. acc., 16 outs. miss. |

| L2               | 1-Mbyte, 4-way assoc., WB,          |

|                  | 10-cy. access, 16 outs. misses      |

| L1/L2 bus        | Runs at processor clock             |

| Line size        | 64 bytes                            |

| L2/Mem. Bus      | Split tran. 32-B. 3-cy.+1 arbi.     |

| Memory           | 4-way interl., 100-cy. DRAM         |

| Directory        | Origin-2000 NACK-based MESI         |

| Directory cy.    | 16-cy. (without mem. access)        |

| Interleaving     | 4 cohe. controllers per node        |

| Network          | Pipelined point-to-point net.       |

| Network width    | 8-bytes/flit                        |

| Switch buf. size | 64 flits                            |

| Switch latency   | 4-cy./flit + 4 arbitrat.            |

Cuadro 1: Parámetros de nuestro sistema de simulación

### 4. Resultados experimentales

Nuestras simulaciones se han realizado utilizando RSIM [9]. Los parámetros de la arquitectura simulada aparecen descritos en el Cuadro 1. RSIM ha sido modificado para asignar rangos de direcciones de memoria a los controladores de coherencia usando el algoritmo Round-Robin con granularidad de página. Se utiliza un protocolo de coherencia tipo MESI, similar al del sistema SGI Origin-2000 [6].

La carga de trabajo elegida pertenece al benchmark Splash-2 [12]. Se han elegido aque-

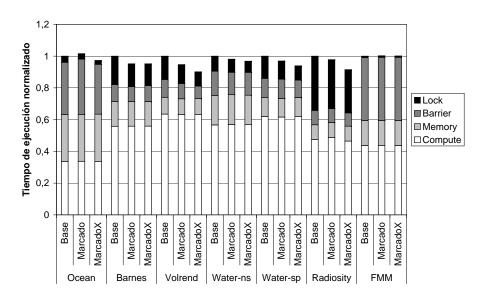

Figura 5: Tiempo de ejecución normalizado para el sistema base y las diferentes técnicas propuestas

llas aplicaciones que presentan contención. Las aplicaciones han sido compiladas con una librería de sincronización de cerrojos basada en  $Test \mathcal{C}(TaS)$  (ver Figura 1) implementada con instrucciones RMW. Las barreras se han implementado con un árbol binario simple. Dichas aplicaciones han sido compiladas garantizando que cada bloque de memoria contenga como mucho una variable del cerrojo. En la aplicación Volrend se ha corregido una barrera que había sido originalmente codificada a mano.

En esta sección comparamos un controlador tipo NACK ("Base"), con un controlador al que hemos aplicando las técnicas propuestas ("Marcado" y "MarcadoX"). Para cada aplicación se muestran dos gráficos: el tiempo de ejecución normalizado (Figura 5) y el número normalizado de TaS (Figura 6). En la Figura 5, se presenta el tiempo de ejecución de la fase paralela de cada aplicación normalizado a Base. El tiempo de ejecución se ha dividido en cuatro categorías. "Lock" se refiere al número de ciclos invertidos en adquirir y devolver la secciones críticas; "Barrier" al número de ciclos utilizados en barreras; "Memory" al número de ciclos utilizados en el acceso a variables com-

partidas dentro y fuera de las secciones críticas, sin incluir ni el acceso a las variables del cerrojo ni el acceso a barreras; finalmente "Compute" indica el número de ciclos restantes.

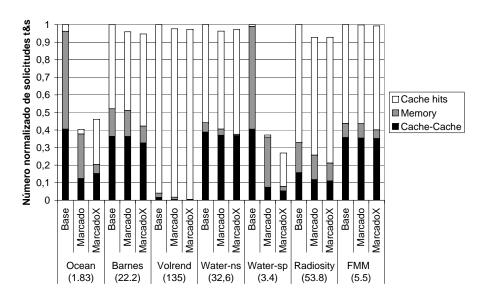

En la Figura 6 se muestra el número de RMW producidos para cada una de las aplicaciones en su fase paralela. Se muestra entre paréntesis el número de TaS por millón de instrucciones ejecutadas. Las columnas están normalizadas a Base y divididas en tres categorías. "Cache-Cache" se refiere al número de RMW que producen una transición cachecache, "Cache Hits" son los RMW que conllevan un acierto en la cache, y "Memory" engloba el resto de RMW.

Del análisis de resultados entre Base y Marcado, podemos extraer las siguientes observaciones:

Las aplicaciones Volrend y Radiosity presentan un número de TaS relevante respecto del número de instrucciones ejecutadas (135 y 53 TaS por millón de instrucciones ejecutadas respectivamente). La técnica del marcado reduce el número de TaS que generan transacciones cache-cache en un 73,6 % en la aplicación

Figura 6: Número de TaS normalizados para el sistema base, la técnica del Marcado y la del Marcado X. Entre paréntesis, el número de TaS por millón de instrucciones ejecutadas

Volrend y en un 25,2% para Radiosity. Esto es debido a que en ambas aplicaciones existen secciones críticas utilizadas por todos los nodos de forma simultánea, dando lugar a contenciones elevadas. Ambas aplicaciones presentan una reducción del 2,2% y del 5,3% respectivamente en su tiempo de ejecución.

- Las aplicaciones Barnes y Water-ns presentan un menor número de solicitudes TaS por millón de intrucciones (22 y 32 respectivamente). La técnica de Marcado sólo consigue reducir el número de TaS que generan transacciones cache-cache en un 0.1% y 4.6% respectivamente. Esto se debe a que ambas aplicaciones utilizan un vector de cerrojos al que se accede mediante una función de hash en Barnes y mediante un identificador de moléculas en Water-ns. En ambos casos el número de nodos que acceden simultáneamente a un mismo cerrojo es pequeño, de ahí la poca efectividad de nuestra técnica. La reducción del tiempo de ejecución es de 4,8 % en Barnes y de 1,9 % en Water-ns.

- La aplicaciones Ocean y Water-sp presentan un número pequeño de TaS por millón de instrucciones ejecutadas. La técnica de Marcado reduce aquellas que generan transacciones cache-cache en un 69,4 % y 81,7% respectivamente. Esto se debe a que en Ocean existen solamente cuatro secciones críticas, pero son utilizadas simultáneamente por todos los nodos dando lugar a una contención elevada. Watersp tiene un comportamiento similar. En Ocean se produce un incremento en el tiempo de ejecución de 1,5 % (debido a un aumento en el desequilibrio de la carga que se refleja en el tiempo de espera en barreras) y en Water-sp una reducción de 3,0 %.

- La aplicación FMM presenta un número de TaS poco relevante, 5,5 por millón de instrucciones. Nuestra técnica apenas reduce en un 0,9 % los TaS que generan transacciones cache-cache. La mayor parte de las secciones críticas en esta aplicación se corresponde con un vector de cerrojos accedido a través de una función hash, generando poca contención.

El tiempo de ejecución se incrementa un 0.2% al aplicar nuestra técnica.

La técnica de Marcado Exclusivo reduce el número de TaS con respecto al sistema base, e incrementa además el número de aciertos en la cache local, entre un  $0.8\,\%$  en Volrend y un  $1\,938\,\%$  en Water-sp. Estos resultados se corresponden con el objetivo de esta técnica consistente en incrementar el número de aciertos en la caché local de las instrucciones TaS (ver Sección 3.3). El tiempo de ejecución se reduce entre un  $2.7\,\%$  en Ocean y un  $9.8\,\%$  en Volrend, excepto para la aplicación FMM que apenas sufre variación.

### 5. Conclusiones

En este trabajo se ha explorado una de las posibles causas de contención en el cambio de propietario de un cerrojo sobre sistemas DSM con controladores de coherencia basados en NACK. Mediante el marcado en las solicitudes de liberación de secciones críticas se ha desarrollado una técnica que permite reducir el número de nodos que obtienen una copia del cerrojo en estado abierto, reduciendo así el número de instrucciones TaS ejecutadas fuera del camino crítico. Se consigue una reducción máxima del tiempo de ejecución de un 9,8 % en el repertorio Splash-2 considerado.

#### 6. Agradecimientos

Los autores de este trabajo agradecen al Ministerio de Ciencia y Tecnología su apoyo a través del Proyecto TIN2004-07739-C02-02 y a la Junta de Castilla y León a través del Proyecto de Investigación VA031B06.

### Referencias

M. Chaudhuri and M. Heinrich. The impact of negative acknowledgments in shared memory scientific applications. *IEEE Trans. Pa*rallel Distrib. Syst., 15(2):134-150, 2004.

- [2] P. Damron, A. Fedorova, Y. Lev, V. Luchangco, M. Moir, and D. Nussbaum. Hybrid transactional memory. In ASPLOS-XII, pages 336–346, New York, NY, USA, 2006. ACM Press.

- [3] A. de Dios, B. Sahelices, P. Ibáñez, V. Viñals, and J. Llabería. Speeding-up synchronizations in DSM multiprocessors. In Euro-Par, pages 473–484, 2006.

- [4] J. R. Goodman, M. K. Vernon, and P. J. Woest. Efficient synchronization primitives for large-scale cache-coherent multiprocessors. In ASPLOS-III, pages 64-75, New York, NY, USA, 1989. ACM Press.

- [5] A. Kägi, D. Burger, and J. R. Goodman. Efficient synchronization: let them eat QOLB. In ISCA '97, pages 170–180, New York, NY, USA, 1997. ACM Press.

- [6] J. Laudon and D. Lenoski. The sgi origin: A CC-NUMA highly scalable server. In ISCA, pages 241-251, 1997.

- [7] D. Lenoski, J. Laudon, T. Joe, D.Ñakahira, L. Stevens, A. Gupta, and J. L. Hennessy. The DASH prototype: Logic overhead and performance. *IEEE Trans. Parallel Distrib. Syst.*, 4(1):41-61, 1993.

- [8] J. F. Martinez and J. Torrellas. Speculative locks for concurrent execution of critical sections in shared-memory multiprocessors. Technical report, Champaign, IL, USA, 2001.

- [9] V. S. Pai, P. Ranganathan, and S. V. Adve. Rsim reference manual. version 1.0. Technical Report 9705, Electrical and Computer Engineering Dept., Rice University, July 1997.

- [10] Z. Radović and E. Hagersten. Hierarchical Backoff Locks for Nonuniform Communication Architectures. In HPCA-9, pages 241– 252, Anaheim, California, USA, feb 2003.

- [11] R. Rajwar, A. Kägi, and J. R. Goodman. Improving the throughput of synchronization by insertion of delays. In HPCA, pages 168–179, 2000.

- [12] S.C. Woo, M. Ohara, E. Torrie, J.P. Singh, and A. Gupta. The splash-2 programs: characterization and methodological considerations. SIGARCH Comput. Archit. News, 23(2):24-36, May 1995.