# Universidad de Valladolid

ESCUELA TÉCNICA SUPERIOR DE INGENIERÍA INFORMÁTICA

DEPARTAMENTO DE INFORMÁTICA

TESIS DOCTORAL:

# Hierarchical Transparent Programming for Heterogeneous Computing

Presentada por **D. Yuri Torres de la Sierra** para optar al grado de doctor por la Universidad de Valladolid

Dirigida por:

Dr. Arturo González Escribano Dr. Diego R. Llanos Ferraris

Mayo 2014

ii

#### Resumen

La computación paralela y el desarrollo de programas paralelos intentan reducir el tiempo de ejecución de las aplicaciones. Durante años, las optimizaciones de códigos secuenciales fueron diseñadas sin tener en cuenta la paralelizacion de datos ni de las tareas. Actualmente, los dispositivos multi-core se han vuelto omnipresentes en nuestras máquinas de cómputo, haciendo que la paralelización tome un papel aún más importante. La computación paralela está estrechamente relacionada tanto con el hardware como con el software. El objetivo final de la computación paralela es mejorar, en la medida de lo posible, la capacidad computacional de las máquinas.

El constante crecimiento en el rendimiento de las Unidades de Procesamiento Gráfico (GPUs), junto con recientes mejoras en su programabilidad, ha hecho que estos dispositivos sean una buena opción como aceleradores hardware en la Computación de Altas Prestaciones (HPC) para una variedad de aplicaciones.

La noción de la computación heterogénea ha emergido hace muy pocos años. Este concepto se basa en explotar un sistema compuesto por dispositivos de naturaleza diferente. Los sistemas heterogéneos pueden estar formados por procesadores con múltiples núcleos, GPUs y procesadores reconfigurables entre otros. Aunque el uso de sistemas heterogéneos, para aprovechar al máximo toda la capacidad computacional, pueda resultar una idea interesante, su complejidad de programación se encuentra un paso por delante de la programación paralela. Los principales problemas que aparecen son los siguientes: el primer problema es la necesidad de escribir código propios tanto para los núcleos de la CPU como para la GPU y el segundo problema, es la distribución de carga de trabajo entre los diferentes dispositivos, ya que estos sistemas no comparten un espacio de direcciones común. Además, cada dispositivo presenta diferentes capacidades de cómputo, por lo que cada uno es capaz de trabajar a ritmo diferente.

Durante la última década, se han propuesto diferentes modelos de programación con el objetivo de manejar la complejidad de las particiones y mapeo multinivel de datos. Estos modelos de programación pueden caer en dos categorías: aquellos que esconden las comunicaciones subyacentes y aquellos en donde las comunicaciones son impulsadas por las particiones creadas por el usuario. Estos modelos de programación paralela no ayudan al programador a expresar de forma explícita el modelo de comunicación que necesita el algoritmo independientemente de la partición de datos elegida. El Tiling es una técnica conocida que es usada para distribuir datos y tareas en programas paralelos y mejorar la localidad de bucles anidados en códigos secuenciales. El uso de estructuras de datos para soportar tiling, permite explotar eficientemente la jerarquía de memoria ya que a menudo los datos son reutilizados dentro del tile.

Trasgo es un framework de programación que está siendo desarrollado por nuestro grupo de investigación de la Universidad de Valladolid. Trasgo se basa en especifica-

ciones de alto nivel y paralelismo anidado, permitiendo expresar de forma sencilla varias combinaciones de paralelismo de tareas con un esquema común. El back-end de Trasgo es soportado por Hitmap, una biblioteca runtime para el tiling jerárquico y el mapeo de arrays. Hitmap implementa funciones para crear, manipular, mapear y comunicar tiling-arrays jerárquicos.

En esta tesis doctoral estudiamos la posibilidad de desarrollar un sistema de programación portable y transparente que incorpore tiling jerárquico y políticas de scheduling con el objetivo de aprovechar las capacidades de la computación heterogénea.

Para abordar nuestra propuesta de investigación hacemos uso de la biblioteca Hitmap como un framework prototipo. Este framework permite explotar sistemas de memoria distribuida. En este trabajo extendemos de forma conceptual y práctica este framework para aprovechar todos los recursos hardware (CPU-GPU) en entornos heterogéneos. Además, éste permite generar códigos abstractos que a su vez son transparentemente adaptados para sistemas con diferentes tipos de dispositivos.

Para ello es necesario también un estudio de las arquitecturas GPU que ayude a determinar unos buenos valores de los parámetros de configuración GPU (la geometría/tamaño de los bloques de hilo o la configuración de la cache L1) que deberían ser escogidos de otra forma por el programador. El conocimiento obtenido de este estudio es usado para crear políticas de selección de dichos valores. Estas políticas son incluidas en la biblioteca Hitmap.

Tras examinar y analizar los resultados experimentales concluimos que es factible la creación de un sistema de programación que incorpore técnicas de particionado de datos, herramientas de comunicación, y selección trasparente para el programador de buenos valores de los parámetros de configuración GPU para sistemas heterogéneos.

#### **Palabras clave**

APSP, herramientas de mapeo automático, tuneado automático de código, benchmarking, kernels concurrentes, CUDA, mapeo de datos, particionado de datos, Dijkstra, Fermi, GPU, GP-GPU, dispositivos heterogéneos, sistemas heterogéneos, Kepler, técnicas de mapeo, micro benchmarks, restricciones de tamaño de memoria, MPI, NSSP, OpenCL, OpenMP, algoritmos paralelos, bibliotecas paralelas, medición de rendimiento, modelo poliédrico, SSSP, geometría del bloque de hilos, tiling.

#### Abstract

Parallel computing and the development of parallel programs is a way to reduce the time of the program execution. During many years, sequential optimization was designed without thinking about parallel tasks. Currently, multi-core devices have arrived, making code parallelization more important. The parallel computing is closely related with both hardware and software point of view, in both cases, many calculations are carried out simultaneously. The final objective of parallel computing is the improvement in computing capacity.

The rapid increase in the performance of Graphics Processing Units (GPUs), coupled with recent improvements in its ease of programming, have made graphics hardware a compelling platform for High Performance Computing field (HPC) in a wide kind of applications. For this impressive processing potential, a single GPU has the sufficient power to compete with many super-scalar CPUs.

The heterogeneous computing notion has emerged few years ago. This concept references to exploit a system composed by multiple mixed compute devices. A Heterogeneous system can be composed by commodity multi-core processors, graphics processors and reconfigurable processors among others. Although the use of heterogeneous systems to take maximum advantage of all computing capabilities may seem a natural idea, their programming complexity is also one step beyond of the intrinsically complex parallel programming. Two main problems appear. First, the need of writing specialized code for both the CPUs cores and GPUs or other accelerators that are present in the system. Second, the problems related with data distribution among devices, and the associated load-balancing problem since heterogeneous systems do not share a common address space and present different computing powers.

During the last decade, different programming models have been proposed to handle the complexity of multilevel data partition and mapping. These programming models roughly falls into two categories: Those that hide the underlying communications, and those where the explicit communication is driven by the partition made by the user. These parallel programming models do not help the programmer to explicitly express the communication pattern needed by the algorithm regardless of the data partition chosen. Tiling is a well-known technique used to distribute data and task in parallel programs and to improve the locality of nested loops in sequential code. The use of data structures to support tiles allows to better exploit the memory hierarchy, since data is often reused withing a tile.

Trasgo is a programming framework that is being developed by our Trasgo research group at the University of Valladolid (Spain). Trasgo is based on high-level and nestedparallel specifications allowing easily express several complex combinations of data and parallelism tasks with a common scheme. One of the most important features is that this model hides the layout and scheduling details. The Trasgo back-end is supported by Hitmap, a runtime library for hierarchical tiling and mapping of arrays. The Hitmap library implements functions to efficiently create, manipulate, map, and communicate hierarchical tiling arrays.

In this Ph.D. thesis we study the possibility of developing a portable and transparent programming system that incorporates hierarchical tiling and scheduling policies in order to take advantage of heterogeneous computing capabilities.

To accomplish our research proposal we take profit the of Hitmap library. Hitmap is used as a prototype framework that integrates a parallel computation model which takes profit of all available hardware resources (CPU-GPU) in heterogeneous environments. This framework allows to generate abstract codes which are transparently adapted to heterogeneous systems with mixed types of accelerator devices.

We present a study of the GPU architectures to help to determine good values of configuration parameters that should be chosen by the programmer. The knowledge obtained from this study is used to create proper policies of selecting configuration parameters values of GPU devices, such as, threadblock geometry/size and the configuration of L1. These policies are included in previous framework.

After examining and analyzing the experimental results, we consider the feasibility of creating a programming execution containing automatic data partitioning techniques, communication tools, and select transparently to the programmer, good values of GPU configuration parameters for heterogeneous systems.

#### Keywords

APSP, automatic mapping tools, automatic code tuning, benchmarking, concurrent kernel, CUDA, data layout, data partition, Dijkstra, Fermi, GPU, GP-GPU, heterogeneous devices, heterogeneous systems, Kepler, mapping techniques, micro-benchmarks, memory-size restrictions, MPI, NSSP, OpenCL, OpenMP, parallel algorithms, parallel libraries, performance measurement, polyhedral model, SSSP, threadblock geometry, tiling.

A mis padres, Ramón y Eva, y a mi hermano José Ramón, con gratitud y gran admiración. viii

## Acknowledgments

After all these years of work, insomnia, work, fun, work, challenges, conferences, and..., work, here it is, my Thesis is finally completed. It has been a long, tough way, but if I could come back in time, I would definitely not change it for anything. Becoming a PhD has been my dream during the last four years, and during this long way I have found a lot of people that have helped me to make this dream come true.

First of all, I am deeply indebted to my supervisors, Dr. Arturo González Escribano and Dr. Diego R. Llanos Ferraris, for guiding me throughout the process of becoming a PhD. None of this would have taken place without the help and support of my supervisor, advisor, mentor, and friend Dr. Arturo González Escribano. Thanks a lot for guiding me, for the daily interaction, and for all your commitment, successful advises, and critical questions. I also owe thanks to my supervisor Dr. Diego R. Llanos Ferraris for all the work and fruitful discussions that challenged me, and for showing me the best way to achieve my goals.

I want to thank my colleagues from the Trasgo Group at University of Valladolid (Álvaro, Ana, Héctor, Javier, and Sergio). Sharing my time and experiences with you all has been very rewarding.

I want to thank the Universidad de Valladolid fellowships program (Formación Personal Investigador, FPI-2010, aplicación presupuestaria 180.113-541A.2.01-691) for providing me with the financial support necessary to carry out this work, that has been co-funded by *Banco Santander*. Thanks a lot for making it possible. I would like to thank all my friends and dear family. En particular me gustaría dar las gracias a mis padres Ramón y Eva, por todo el amor y cariño, por el esfuerzo y sacrificio, y por responder a todas mis necesidades con un rotundo sí a ojos cerrados. A mi gran amigo David Fernández, nos conocemos de toda la vida, y siempre me ha apoyado en todo de forma incondicional, por ello, le estaré eternamente agradecido. Muchas Gracias.

> Yuri Torres Valladolid, 2014

# Contents

| 0 | Resu | umen de    | Tesis                                  | 1 |

|---|------|------------|----------------------------------------|---|

|   | 0.1  | Objetiv    | o de la investigación                  | 1 |

|   |      | 0.1.1      | Pregunta de investigación              | 1 |

|   |      | 0.1.2      | Tareas                                 | 1 |

|   |      | 0.1.3      | Metodología de investigación           | 2 |

|   | 0.2  | Contrib    | buciones y conclusiones                | 2 |

|   |      | 0.2.1      | Contribuciones                         | 3 |

|   |      | 0.2.2      | Conclusiones                           | 5 |

|   |      | 0.2.3      | Trabajo futuro                         | 6 |

| 1 | Intr | oduction   | 1 7                                    | 7 |

|   | 1.1  | Context    | t                                      | 7 |

|   |      | 1.1.1      | Parallel computing                     | 7 |

|   |      | 1.1.2      | Multi- and manycore architectures      | 7 |

|   |      | 1.1.3      | GPUs for parallel computing            | 8 |

|   |      | 1.1.4      | Heterogeneous computing                | 9 |

|   |      | 1.1.5      | Parallel programming and tiling models | ) |

|   |      | 1.1.6      | The Trasgo programming framework       | ) |

|   |      | 1.1.7      | The Hitmap run-time library            | 1 |

|   | 1.2  | Purpose    | e of this research                     | 1 |

|   |      | 1.2.1      | Research question                      | 1 |

|   |      | 1.2.2      | Tasks                                  | 1 |

|   |      | 1.2.3      | Research methodology                   | 2 |

|   | 1.3  | Outline    |                                        | 3 |

| 2 | Stat | e of the A | Art 15                                 | 5 |

|   | 2.1  | Program    | mming tools for heterogeneous systems  | 5 |

|   |      | 2.1.1      | Programming languages for GPUs         | 5 |

#### CONTENTS

|   |     | 2.1.2  | GPU tuning strategies                                | 16 |

|---|-----|--------|------------------------------------------------------|----|

|   | 2.2 | Challe | enges in heterogeneous programming                   | 18 |

|   |     | 2.2.1  | Data partition and load balancing techniques         | 18 |

|   |     | 2.2.2  | Memory size restrictions                             | 19 |

|   |     | 2.2.3  | Tiling support                                       | 19 |

|   | 2.3 | Bench  | marking                                              | 20 |

|   |     | 2.3.1  | Micro-Benchmarking for GPUs                          | 20 |

|   |     | 2.3.2  | Choice of benchmarks used in this work               | 21 |

| 3 | The | Hitmaj | p Library for Homogeneous Systems                    | 23 |

|   | 3.1 | Overv  | iew                                                  | 24 |

|   |     | 3.1.1  | Functionalities                                      | 24 |

|   |     | 3.1.2  | Notations                                            | 25 |

|   | 3.2 | Tiling | functionalities                                      | 26 |

|   | 3.3 | Mappi  | ing and communication functions                      | 27 |

|   |     | 3.3.1  | Combinations of topology and layout functions        | 28 |

|   | 3.4 | Design | n and implementation                                 | 30 |

|   |     | 3.4.1  | Tiling classes                                       | 30 |

|   |     | 3.4.2  | Data partition and mapping subsystem                 | 32 |

|   |     | 3.4.3  | Topologies                                           | 32 |

|   |     | 3.4.4  | Layouts overview                                     | 33 |

|   |     | 3.4.5  | Layout plug-ins implementation                       | 33 |

|   |     | 3.4.6  | Groups and hierarchical partitions                   | 35 |

|   |     | 3.4.7  | Topology and layout techniques currently implemented | 35 |

|   |     | 3.4.8  | Communications implementation                        | 36 |

|   | 3.5 | Experi | imental evaluation of Hitmap                         | 37 |

|   |     | 3.5.1  | Design of experiments                                | 37 |

|   |     | 3.5.2  | Performance comparison                               | 38 |

|   | 3.6 | Conclu | usions                                               | 44 |

| 4 | New | Abstra | action Layers for an Heterogeneous Hitmap            | 45 |

|   | 4.1 | Mappi  | ing synchronization issues                           | 45 |

|   |     | 4.1.1  | Conceptual approach                                  | 45 |

|   |     | 4.1.2  | Design and implementation                            | 47 |

|   |     | 4.1.3  | Mapping and synchronization issues: Summary          | 49 |

|   | 4.2 | Memo   | bry size restrictions                                | 50 |

|   |     | 4.2.1  | Model for parallel computations                      | 51 |

|   |     | 4.2.2  | Partition of regular computations                    | 53 |

|   |     | 4.2.3  | Memory size-restrictions: Summary                    | 57 |

#### CONTENTS

|   | 4.3  | Concl          | usions                                               | 57         |

|---|------|----------------|------------------------------------------------------|------------|

| 5 | Stuc | lv of G        | PU Configuration Parameters                          | 59         |

|   | 5.1  | -              | dblock geometry                                      | 59         |

|   |      | 5.1.1          | Threadblock size and occupancy tradeoff              | 59         |

|   |      | 5.1.2          | Shape in several dimensions                          | 62         |

|   |      | 5.1.3          | Tuning techniques and threadblock size and shape     | 63         |

|   |      | 5.1.4          | ThreadBlock size and shape in OpenCL                 | 63         |

|   | 5.2  | Exper          | imental study                                        | 64         |

|   |      | 5.2.1          | Setup                                                | 64         |

|   |      | 5.2.2          | Benchmarks with coalesced accesses                   | 65         |

|   |      | 5.2.3          | Benchmarks with non-coalesced accesses               | 67         |

|   |      | 5.2.4          | Experimental results                                 | 67         |

|   |      | 5.2.5          | Limitations of this experimental study               | 75         |

|   | 5.3  | Micro          | -benchmarks (uBench)                                 | 75         |

|   |      | 5.3.1          | The uBench suite                                     | 75         |

|   |      | 5.3.2          | uBench evaluation                                    | 82         |

|   |      | 5.3.3          | Summary                                              | 87         |

|   | 5.4  | Concl          | usions                                               | 87         |

| 6 | Ехр  | erimen         | tal Evaluation of an Heterogeneous Hitmap            | 89         |

|   | 6.1  |                | ing and synchronization issues                       | 89         |

|   |      | 6.1.1          | Case study                                           | 89         |

|   |      | 6.1.2          | Experimental work                                    | 92         |

|   |      | 6.1.3          | Synchronization issues: Conclusions                  | 95         |

|   | 6.2  | Memo           | bry size restrictions                                | 95         |

|   |      | 6.2.1          | Memory size-restrictions: Conclusions                | 98         |

|   | 6.3  | A real         | -world benchmark: The SSSP problem                   | 98         |

|   |      | 6.3.1          | Parallel Dijkstra for GPUs                           | 98         |

|   |      | 6.3.2          | Experimental setup                                   | 102        |

|   |      | 6.3.3          | Experimental results                                 | 105        |

|   |      | 6.3.4          | The SSSP problem: Conclusions                        | 107        |

|   | 6.4  | APSP           | problem                                              | 108        |

|   |      | 6.4.1          | Experimental setup                                   | 108        |

|   |      |                |                                                      |            |

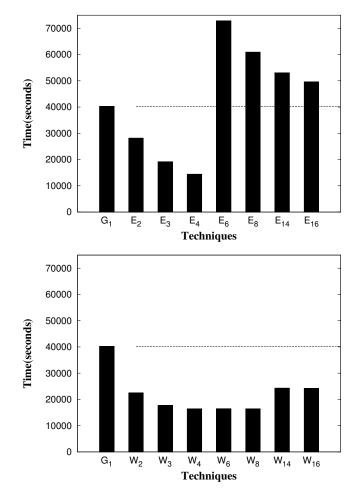

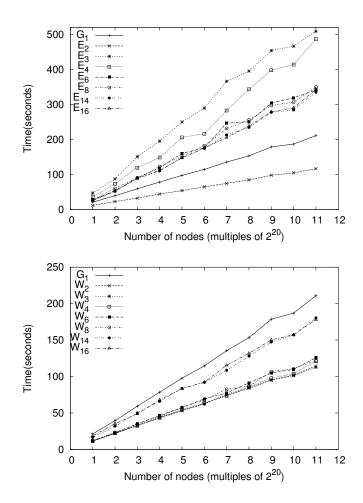

|   |      | 6.4.2          | Experimental results                                 | 109        |

|   |      | 6.4.2<br>6.4.3 | Experimental results       APSP-problem: Conclusions |            |

|   | 6.5  | 6.4.3          | •                                                    | 111        |

|   | 6.5  | 6.4.3          | APSP-problem: Conclusions                            | 111<br>111 |

xiii

#### CONTENTS

|   |             | 6.5.3    | Target architectures                   |  |

|---|-------------|----------|----------------------------------------|--|

|   |             | 6.5.4    | Input set characteristics              |  |

|   |             | 6.5.5    | Load-balancing techniques evaluated    |  |

|   |             | 6.5.6    | Experimental results                   |  |

|   |             | 6.5.7    | Load balancing techniques: Conclusions |  |

| - | C           | clusions | 110                                    |  |

| 7 |             |          |                                        |  |

|   | 7.1         |          | ary of contributions                   |  |

|   | 7.2         |          | nsions                                 |  |

|   | 7.3         | Future   | directions                             |  |

| A | CUI         | DA Prog  | gramming Model 123                     |  |

|   | A.1         | CUDA     | model                                  |  |

|   |             | A.1.1    | Brief examples                         |  |

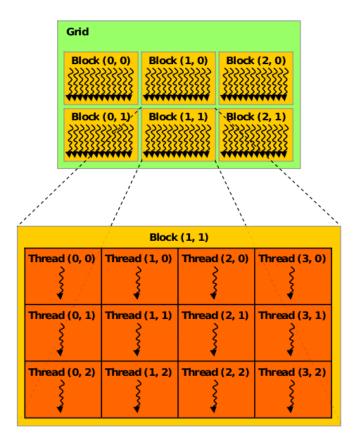

|   |             | A.1.2    | Thread organization                    |  |

|   |             | A.1.3    | Synchronization barriers               |  |

|   |             | A.1.4    | Memory accesses                        |  |

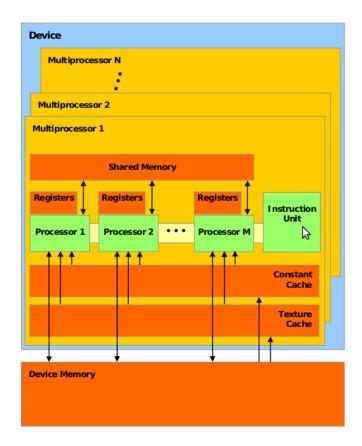

|   |             | A.1.5    | CUDA architecture                      |  |

|   | A.2         | Concu    | rrent kernels                          |  |

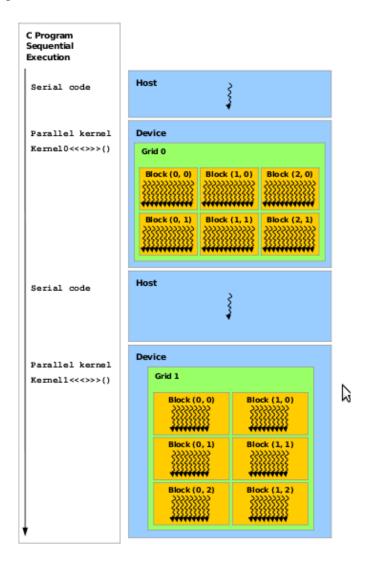

|   | A.3         | CUDA     | heterogeneous programming              |  |

|   | A.4         | CUDA     | strengths and weaknesses               |  |

|   |             | A.4.1    | Advantages                             |  |

|   |             | A.4.2    | Constraints                            |  |

|   |             | A.4.3    | Summary                                |  |

|   | A.5         | Review   | v of NVIDIA GPUs architectures         |  |

| р | D           |          | 125                                    |  |

| B | -           | chmark   |                                        |  |

|   | <b>B</b> .1 |          | -matrix multiplication                 |  |

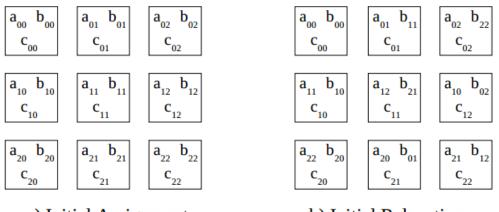

|   | D A         | B.1.1    | Cannon's algorithm                     |  |

|   | B.2         |          | st Path Problem                        |  |

|   |             | B.2.1    | Graph Theory Notation                  |  |

|   |             | B.2.2    | Dijkstra's Algorithm                   |  |

|   |             | B.2.3    | Parallel Dijkstra                      |  |

|   |             | B.2.4    | SSSP problem                           |  |

|   |             | B.2.5    | APSP problem                           |  |

# List of Figures

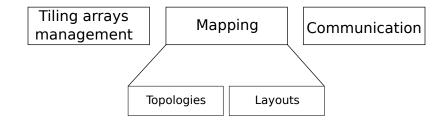

| 3.1  | Hitmap library functionalities                                         | 24  |

|------|------------------------------------------------------------------------|-----|

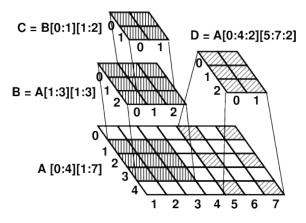

| 3.2  | Tiling creation from an original array                                 | 26  |

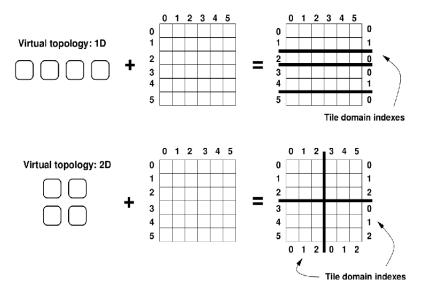

| 3.3  | Partitions computed for different virtual processor topologies         | 29  |

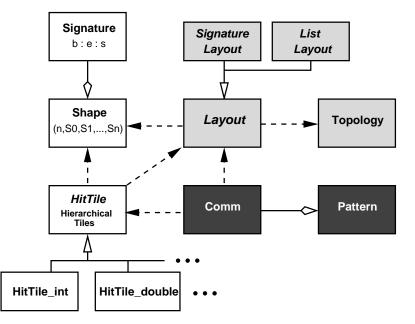

| 3.4  | UML diagram of the architecture of the Hitmap library                  | 30  |

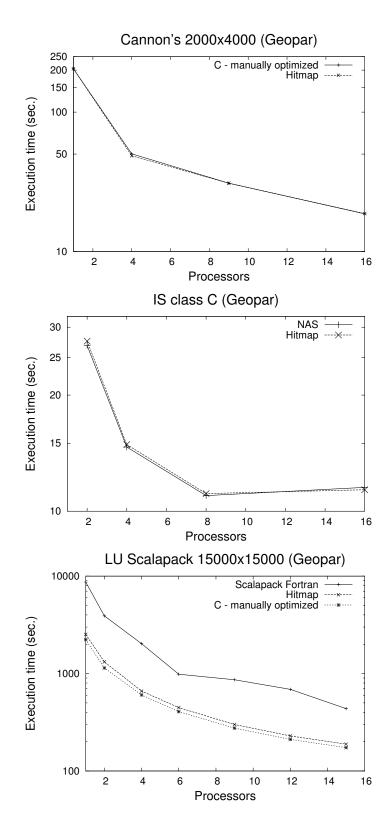

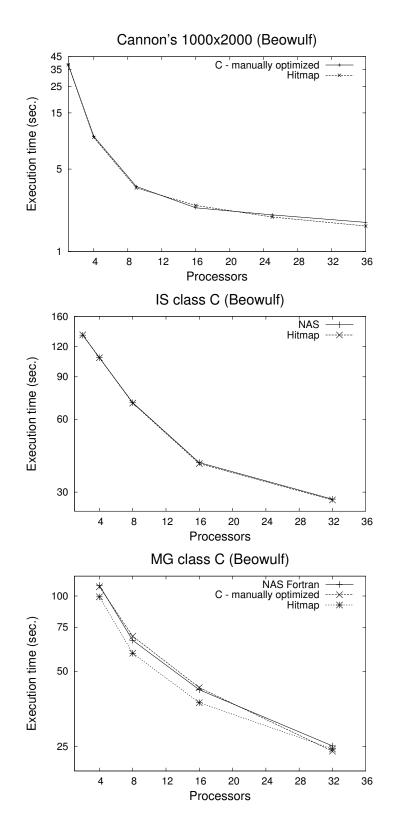

| 3.5  | Performance results for MG benchmark                                   | 39  |

| 3.6  | Performance results for some parallel kernels in a Beowulf cluster     | 40  |

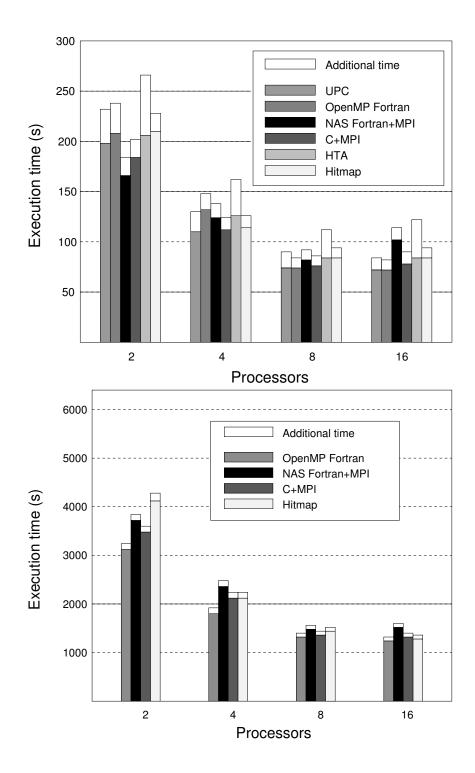

| 3.7  | NAS MG benchmark performance comparison                                | 42  |

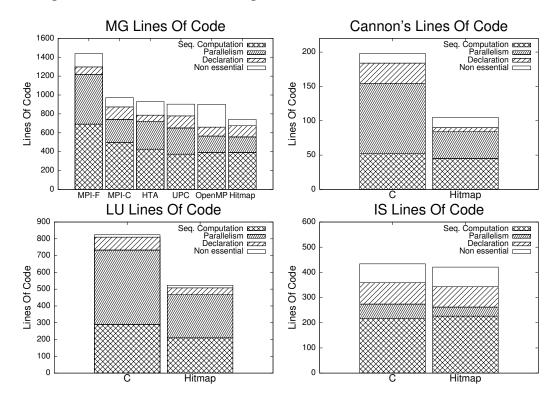

| 3.8  | Comparison of code lines                                               | 43  |

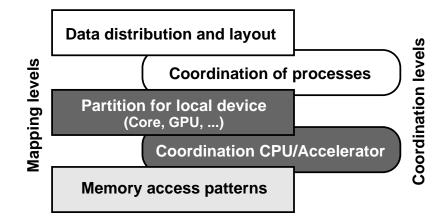

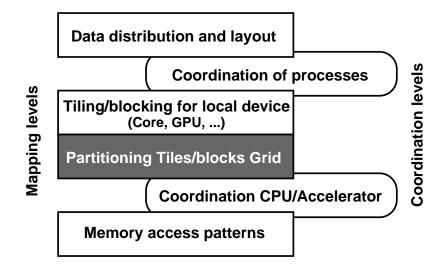

| 4.1  | Mapping/Coordination levels of Hitmap                                  | 46  |

| 4.2  | Mapping/Coordination levels Hitmap including automatic partition       | 51  |

| 4.3  | Algorithms for the three cases studied                                 | 55  |

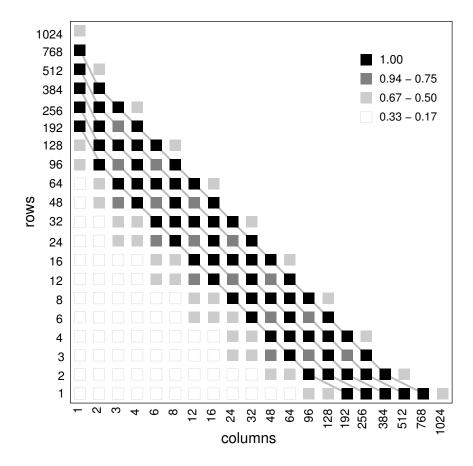

| 5.1  | Maximum Occupancy for different threadblock shapes                     | 62  |

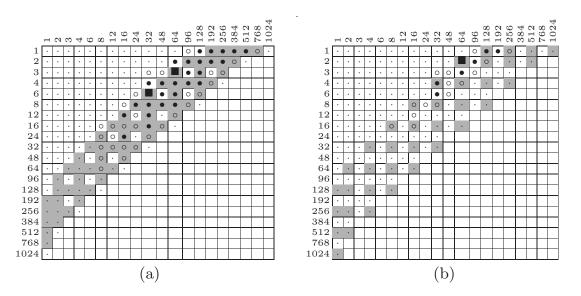

| 5.2  | Example of diagrams for results tables for uBench-1                    | 83  |

| 6.1  | Heterogeneous Hitmap implementation of Cannon's matrix multiplication  | 90  |

| 6.2  | Load balancing layout scheme in the Cannon's example                   | 91  |

| 6.3  | Hitmap abstraction results (1st part)                                  | 93  |

| 6.4  | Hitmap abstraction results (2nd part)                                  | 94  |

| 6.5  | Execution times for Vector addition, Stencil and MM multiplication     | 96  |

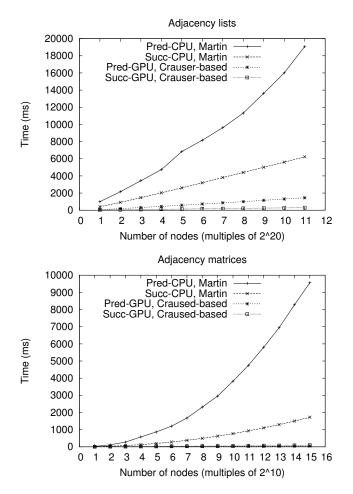

| 6.6  | CPU-Martín vs. our Crauser-based GPU execution times (1st part)        | 104 |

| 6.7  | GPU-Martín vs. our Crauser-based GPU execution times (2st part)        | 105 |

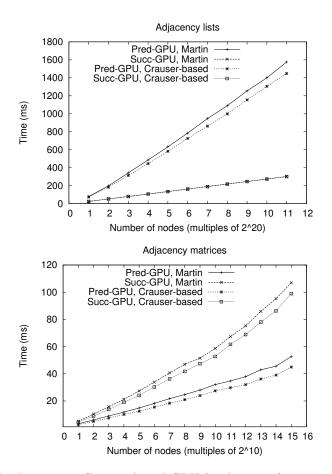

| 6.8  | Total vs. Number of Working Threads in the relax kernel                | 106 |

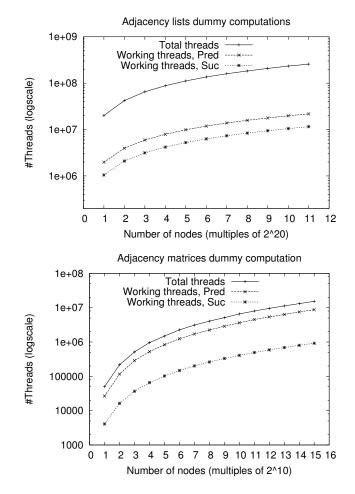

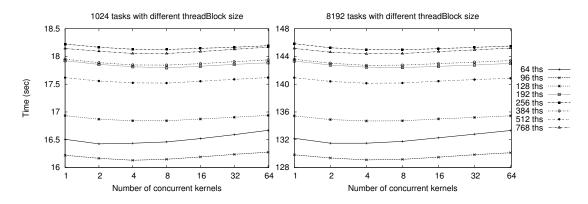

| 6.9  | Relax-kernel execution times for different input sets                  | 110 |

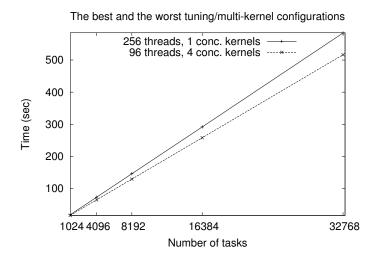

| 6.10 | Execution times of the relax kernel for the best/worst configurations  | 110 |

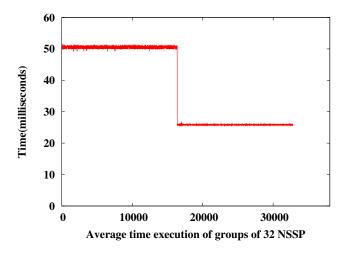

| 6.11 | Temporal cost of the different source nodes for the Kepler GPU         | 113 |

| 6.12 | Execution times of Equitable and Numbered Ticket Scheduling policies . | 115 |

| 6.13 | Execution times of Equitable and Numbered Ticket Scheduling            | 117 |

|      |                                                                        |     |

| A.1 | Computing $Y \leftarrow Ax + y$ in CUDA parallel model                                                                                                                | 5 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| A.2 | Parallel sum reduction tree                                                                                                                                           | 6 |

| A.3 | Grid of threadblocks                                                                                                                                                  | 7 |

| A.4 | A set of SIMT multiprocessors with on-chip shared memory 12                                                                                                           | 9 |

| A.5 | Heterogeneous Programming                                                                                                                                             | 1 |

| A.6 | Fermi memory hierarchy (NVIDIA GTX-480)                                                                                                                               | 3 |

| D 1 |                                                                                                                                                                       |   |

| B.1 | $3 \times 3$ Data Location for Cannon's Algorithm $\dots \dots \dots$ | 6 |

# List of Tables

| 3.1         | Complexity metrics and development effort for the benchmarks considered | 44  |

|-------------|-------------------------------------------------------------------------|-----|

| 5.1         | Execution times for the benchmarks considered in Fermi (A,B,1st)        | 69  |

| 5.2         | Execution times for the benchmarks considered in Fermi (B,C,1st)        | 70  |

| 5.3         | Execution times for the benchmarks considered in Fermi (E,1st)          | 71  |

| 5.4         | Execution times for the benchmarks considered in Fermi (2nd)            | 72  |

| 5.5         | Naïve matrix multiplication: L1 Cache misses                            | 73  |

| 5.6         | uBench classification, according to the criteria proposed               | 82  |

| 6.1         | Martín et al. CPU Versions vs. our GPU Implementation speed-ups         | 105 |

| 6.2         | Comparison between Martín et al. GPU Versions vs. our GPU ones          | 106 |

| 6.3         | Experimental instances                                                  | 114 |

| <b>A</b> .1 | Summary of CUDA architecture parameters (pre-Fermi, Fermi and Kepler)   | 134 |

#### LIST OF TABLES

xviii

# Chapter 0

# Resumen de Tesis

Este documento presenta mi tesis doctoral. Me inicié en paralelización en 2009 y desde entonces siempre intento superarme en este complicado pero a la vez apasionante mundo.

## 0.1 Objetivo de la investigación

#### 0.1.1 Pregunta de investigación

Es posible desarrollar un sistema de programación portable y transparente que incorpore tiling jerárquico y políticas de scheduling con el objetivo de aprovechar las capacidades de la computación heterogénea?

#### 0.1.2 Tareas

Con el objetivo de responder a la pregunta de investigación, hemos llevado a cabo las siguientes tareas:

- A partir de Hitmap, un framework que incorpora tiling y scheduling para sistemas de memoria distribuida, se han estudiado las modificaciones conceptuales y prácticas necesarias para dar soporte a Hitmap en entornos heterogéneos.

- Este estudio muestra la necesidad de nuevos niveles de particionado y sus políticas asociadas. Estas políticas incluyen mecanismos para:

- 1. Mover datos de forma transparente entre los diferentes dispositivos.

- 2. Realizar subdivisiones de tareas que encajen de forma adecuada en la memoria de cada dispositivo.

- 3. Seleccionar tamaños y geometrías para los conjuntos de hilos.

#### 0.1.3 Metodología de investigación

Con el fin de lograr los objetivos propuestos en este documento, seguiremos la metodología de investigación definida por un método de investigación para ingeniería [2]. Este método establece cuatro fases diferentes que el proceso de investigación debe seguir. Cada fase puede repetirse de forma cíclica con el objetivo de redefinir las soluciones propuestas.

- Observar las soluciones existentes. Esta fase tiene el propósito de detectar problemas que serán alcanzados durante el proceso de investigación comenzando con la solución existente. Esto conlleva un completo estudio del estado del arte con el objetivo de encontrar trabajos relacionados con nuestro foco de investigación. Este estudio es presentado en este documento.

- Proponer mejores soluciones. En esta fase se propone una solución que aborde las limitaciones encontradas en la fase anterior. Como mostraremos a lo largo de este trabajo, existe una carencia de frameworks que encapsulen técnicas de particionado y mapeo de datos para entornos heterogéneos, que a su vez, exploten de forma automática y transparente los recursos hardware de los dispositivos GPU. Este trabajo está estrechamente relacionado con la arquitectura de las GPUs. Proponemos varias políticas para (a) seleccionar buenos valores para los parámetros de configuración GPU (tamaño/geometría de los bloques de hilos y la configuración de la cache L1 entre otros) para algunos tipos de aplicaciones y (b), explotar de forma eficiente un balanceo de carga sobre los sistemas heterogéneos.

- *Construir o desarrollar la solución*. La solución propuesta en la fase anterior es implementada en la fase actual. Hemos llevado a cabo un estudio sobre las arquitectura de la GPU y como ayudar al programador a determinar unos buenos valores de los parámetros de configuración. También hemos desarrollado un framework de programación para estudiar la factibilidad de las soluciones propuestas.

- *Medir y analizar la nueva solución*. Finalmente, este método ingenieril establece que la solución propuesta tiene que resolver los problemas descubiertos en la primera fase. Hemos evaluado el sistema usando tanto bancos de pruebas sintéticos como aplicaciones reales.

### 0.2 Contribuciones y conclusiones

En este trabajo de Tesis se ha estudiado la viabilidad de desarrollar un sistema de programación portable y transparente que incorpore tiling jerárquico y políticas de scheduling con el objetivo de aprovechar las capacidades de la computación heterogénea. Para ello hemos presentado un prototipo de framework que encapsula la elección de (a) buenos valores de los parámetros de configuración para dispositivos heterogéneos, (b) estructuras de datos tile, funciones de mapeo y balanceo de carga y (c), funciones de sincronización/comunicación entre dispositivos heterogéneos CPU-GPU. Finalmente, se realiza una evaluación experimental del prototipo de framework con el objetivo de contestar la pregunta de investigación propuesta en esta Tesis.

#### 0.2.1 Contribuciones

#### Primera

Hemos contribuido al desarrollado Hitmap. Se trata de una biblioteca software diseñada para desacoplar los patrones de comunicación del particionado de datos gracias al uso de expresiones abstractas de comunicación. Estas abstracciones son automáticamente adaptadas en tiempo de ejecución dependiendo de la partición. Podemos usar las abstracciones desarrolladas para Hitmap en sistemas homogéneos para implementar unas nuevas orientadas a entornos heterogéneos.

Arturo Gonzalez-Escribano, Yuri Torres, Javier Fresno, and Diego R. Llanos. An Extensible System for Multilevel Automatic Data Partition and Mapping. Parallel and Distributed Systems, IEEE Trans. on Parallel and Distributed Systems, PP(99):1–1, 2013. [45].

#### Segunda

Hemos proporcionado nuevos conocimientos sobre la relación entre la ocupación, la geometría y el tamaño de bloque de hilos, la configuración de la jerarquía de la memoria cache (en la arquitectura Fermi), y el patrón de acceso a memoria global que presentan los hilos.

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Understanding the impact of CUDA tuning techniques for Fermi. High Performance Computing and Simulation (HPCS), 2011 International Conference on, pages 631–639, 2011. [113].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. CUDA Tuning and Configuration Parameters on FermiArchitectures. Advanced Computer Architecture and Compilation for High Performance and Embedded Systems (ACACES 2011), 2011. [112].

- 4. Yuri Torres, Arturo Gonzalez -Escribano, and Diego R. Llanos. Uso del conocimiento de la arquitectura Fermi para mejorar el rendimiento en aplicaciones CUDA. Actas XXII Jornadas de Paralelismo, 2011. [114].

Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Using Fermi architecture knowledge to speed up CUDA and OpenCL programs. Proc. ISPA'12, Leganes, Madrid, Spain, 2012. [118].

#### Tercera

Hemos introducido una suite de microbenchmarks (llamada uBench) para explorar el impacto sobre el rendimiento de (a) criterios de selección de la geometría y tamaño de los bloques de hilos y (b), las configuraciones y recursos hardware de la GPU. Esta suite de microbenchmarks cubre los detalles hardware de las arquitecturas Fermi y Kepler.

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Measuring the Impact of Configuration Parameters in CUDA Through Benchmarking. The 12th International Conference Computational and Mathematical Methods in Science and Engineering, CMMSE 2012, 2012. [116].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. uBench: Performance Impact of CUDA Block Geometry. Technical Report IT-DI-2012-0001, Depto. Informática, Universidad de Valladolid, Dec 2012. [117].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. uBench: exposing the impact of CUDA block geometry in terms of performance. The Journal of Supercomputing, 65(3):1150–1163, 2013. [120].

#### Cuarta

Hemos desarrollado dos aplicaciones reales (el problema SSSP para encontrar el camino/ruta más corto desde un punto a todos los demás; el problema APSP para encontrar la ruta más corta entre cualquiera de los puntos al resto) con el objetivo de probar y verificar las conclusiones obtenidas en [112, 113, 114, 116, 117, 118, 120].

- Hector Ortega-Arranz, Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. A New GPU-based Approach to the Shortest Path Problem. The 2013 International Conference on High Performance Computing & Simulation, (HPCS 2013), pages 505–511, 2013. [92].

- Hector Ortega-Arranz, Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. A Tuned, Concurrent Multi-Kenel Approach to the APSP problem. The 13th International Conference Computational and Mathematical Methods in Science and Engineering, CMMSE 2013, 2013. [93].

#### Quinta

Hemos presentado un framework de programación extendiendo la biblioteca Hitmap

con el objetivo de analizar la posibilidad de (a) crear un modelo de programación y un framework que encapsulen la elección de unos buenos valores de los parámetros de configuración de GPU y las estructuras de datos, (b) funciones de mapeo y balanceo de carga, y (c), funcionalidades de comunicación/sincronización entre dispositivos heterogéneos CPU-GPU.

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Automatic Data Layout at Multiple Levels for CUDA. The 10th International Conference Computational and Mathematical Methods in Science and Engineering, CMMSE 2010, 2010. [111].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Data partition and syn- chronisation in heterogeneous systems. HPC-EUROPA2 project (project number: 228398) with the support of the European Commission Capacities Area Research Infras- tructures, 2013. [119].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Encapsulated Synchronization and Load-Balance in Heterogeneous Programming. Euro-Par 2012 Parallel Processing, volume 7484 of LNCS, pages 502–513. Springer Berlin Heidelberg, 2012. [115].

- Yuri Torres, Arturo Gonzalez-Escribano, and Diego R. Llanos. Automatic run-time mapping of polyhedral computations to heterogeneous devices with memory-size restrictions. In The 2013 International Conference on Parallel and Distributed Processing Techniques and Applications, 2013. [53].

#### 0.2.2 Conclusiones

Basado en la información, discusiones y resultados que se muestran a lo largo de este trabajo de Tesis, las principales conclusiones son las siguientes:

- El uso de Hitmap promueve programas más abstractos, fáciles de mantener y codificar, manteniendo un buen rendimiento. Esta biblioteca permite lograr rendimientos similares a implementaciones que han sido optimizadas manualmente para kernels y benchmarks conocidos en la comunidad científica. Hitmap reduce significativamente el esfuerzo de programación.

- La elección de los valores de los parámetros de configuración de una GPU está estrechamente relacionada con la implementación particular de la aplicación y la arquitectura del dispositivo. Un análisis combinado del conocimiento de la arquitectura GPU y las características del código implementado (tales como el tipo de patrón de acceso a memoria global, el flujo de carga total por hilo y el ratio de

operaciones lectura-escritura sobre la memoria global) puede ayudar, de forma significativa, a seleccionar unos buenos valores para los parámetros de programación GPU.

Es posible crear un entorno de programación que contenga técnicas de particionado automático, herramientas de comunicación, y seleccionar de forma transparente al usuario buenos valores de los parámetros de configuración GPU para sistemas heterogéneos.

#### 0.2.3 Trabajo futuro

Existen varias cuestiones que nos gustaría abordar. Estos focos definen la orientación futura de este trabajo:

- Estamos planeando realizar un estudio sobre la influencia de los efectos hardware y los parámetros de configuración en otras arquitecturas de GPU, tales como AMD e Intel.

- Actualmente estamos trabajando sobre políticas de mapeo más sofisticadas que exploten de forma más eficiente los procesadores de la CPU y las arquitecturas GPU. Se desea probar y verificar la aplicabilidad de estas técnicas para un conjunto más amplio de problemas incluyendo otros benchmarks conocidos por la comunidad científica y aplicaciones reales.

- Personalmente, tengo curiosidad por estudiar los dispositivos FPGA (Field Programmable Gate Array) ya que su funcionalidad hardware puede ser reconfigurada tantas veces como se dese. Me gustaría automatizar aquellas decisiones que cualquier programador debería de tomar antes de lanzar cualquier función sobre un dispositivo de estas características. Desearía dar soporte a dispositivos FPGAs en nuestro marco de programación.

## Introduction

This document presents my Ph.D. Thesis. I started working on parallelization in 2009, always trying to move forward in this exciting and complicated world. This document summarizes my research efforts.

This chapter briefly introduces the reader in the field, showing both the context and motivation of this work and presenting the research question whose answer constitutes this Ph.D. Thesis.

#### 1.1 Context

#### **1.1.1 Parallel computing**

The basic idea of parallel computing appeared around 1960. From the hardware point of view, at that point vacuum tubes had been replaced with transistors, and computers started to be more manegeable. That was the era of small-scale shared memory multiprocessors, with commercially-available systems made by Burroghs and IBM [30]. Since then, advances in processor architecture, memory systems, and network topologies, made parallel computing ubiquitous. Nowadays, even modest laptops have two or four processors.

Despite their availability, it is still difficult to make several processors to cooperate in carrying out a common task. Even with the huge number of processors available in modern manycore systems, some fundamental constrains such as Amdahl's Law, and practical issues, such as data partitioning coordination, and sharing, limit the performance of massively-parallel systems.

#### **1.1.2** Multi- and manycore architectures

During the first decade of the new century, power and dissipation problems started to limit the clock frequency of single processors. At the same time, new technologies pushed forward the limits on the number of available transistors per square unit. Faced with both situations, the natural choice of computer architects was to integrate in a single chip several copies of a given processor chip design. These resulting systems, called *multicore*, was comparatively simple to implement and manage, not only from the architectural point of view but also with respect to the operating system. Task schedulers were modified to issue processes to all available chips, quickly putting into production all hardware resources if the system have several or many pending tasks. However, multicore technology does not speed up the execution of a single task. On the contrary, multicore chips usually run at a fraction of the clock frequency of the original design, making sequential tasks slower.

The manycore paradigm also benefited from the number of available transistors. However, their design starting point is different. Manycore architectures were only designed with highly parallel applications in mind. They comprises several hundreds of very simple processors, frequently combining several multiprocessor units that internally work with a SIMD (Single Instruction, Multiple Data) execution model. Although manycore systems are even less useful than multicores to execute a single task, their specialized design made them the default choice for massively parallel applications.

#### **1.1.3 GPUs for parallel computing**

The most successful example of manycore architectures are Graphic Processing Units (GPUs). These devices were initially designed to manage floating-point graphical information to be sent to the user's display. Therefore, algorithms that were executed on a GPU had to be mapped into a graphics pipeline.

The search for other uses for the computing power provided by GPU devices, together with the addition of more general processing units per computing element, led in 2007 to the development of the CUDA platform SDK by NVIDIA [78]. The CUDA programming interface allows to express many sophisticated programs with a few, easy-to-understood abstractions. The development of CUDA has boosted the use of GPUs for general purpose (GPGPUs) in the execution of massively-parallel tasks not related with graphic processing.

Despite its popularity, CUDA is not the only choice for GPU programming. There are multiple languages to exploit these devices, such as BrookGPU [19], developed at Stanford University, and, more recently, OpenCL [60], a standard API for programming both GPUs and multi-core CPUs. Other GPGPU languages include Scout [71] for scientific visualization, and Intel Ct [102] for high-throughput architectures. It is interesting to note that both of them, together with Brook, are based on the shape concept introduced by the C\* programming language [97] for the Connection Machine.

Although the different benefits of executing general-purpose applications on GPU devices have widely been recognized [61], in order to exploit efficiently the GPU potential,

#### 1.1. Context

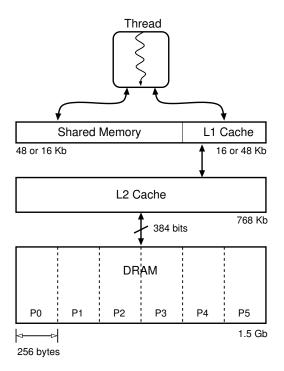

and to predict the power consumption and performance, it is necessary to study in detail the device architecture. In any case, the programmer needs to specify an appropriate threadblock size-shape value for each GPU function, and to define the sizes of sharedand L1 cache memories in order to improve the applications performance. As we will see in this Thesis selecting good values of these GPU configuration parameters hinders even more the GPU programming tasks.

The scalability has been an attractive feature of graphics systems from the beginning. Although the benefits that multiple GPUs can provide are very hard to predict, the possibilities that even a single GPU offers make multi-GPU programming a natural follow-up. Predicting the execution performance of a system composed by multiple GPUs is still a challenge. Some authors, such as Dana Schaa [101], introduce basic models to predict the combined behavior of multiple GPUs in the execution of different applications, by identifying and classifying the major factors that affect their behavior. Other efforts include the Rigel [62] project, that takes into account the different CUDA constrains (such as shared memory utilization, thread fusing, or static work partitioning) to achieve high performance on NVIDIA GPUs.

#### 1.1.4 Heterogeneous computing

The concept of heterogeneous computing [17, 76] is related to the combined use of different kinds of computing resources. It is a step further with respect to what we may call "homogeneous computing", where all processing elements share a common set of characteristics, regardless of the memory organization used (shared or distributed). In heterogeneous computing, systems with different processing capabilities are combined to collaborate in carrying out a given task. A classic example of such computing systems are shared or distributed- memory multiprocessors with GPU devices attached to them.

Although the use of heterogeneous systems to take maximum advantage of all computing capabilities may seem a natural idea, their programming complexity is also one step beyond of the intrinsically complex parallel programming. Two main problems appear. First, the need of writing specialized code for both the CPUs cores and GPUs or other accelerators that are present in the system. Second, the problems related with data distribution among devices, and the associated load-balancing problem since heterogeneous systems do not share a common address space and present different computing powers. All these problems, along with others, make programming for heterogeneous system a piece of craftsmanship, since there is a lack of general-purpose programming frameworks that handle this complexity. This Ph.D. Thesis aims to advance the knowledge needed to solve this problem.

#### **1.1.5** Parallel programming and tiling models

During the last decade, different programming models have been proposed to handle the complexity of multilevel data partition and mapping. These programming models roughly falls into two categories: Those that hide the underlying communications (e.g. Chapel [27], UPC [22]), and those where the explicit communication is driven by the partition made by the user (e.g. MPI). These parallel programming models do not help the programmer to explicitly express the communication pattern needed by the algorithm regardless of the chosen data partition. Parallel programming tools and frameworks presented in the last years do not establish clear boundaries between virtual topologies, domain partitions, and tile management (such as HTA [13] or UPC), or clear boundaries between data management and communications (such as Chapel, UPC or HTA). Such a division of duties would allow the programmer to decouple the communication structures, that depend on the algorithm characteristics, from the data partition mechanisms.

Tiling is a well-known technique used to distribute data and tasks in parallel programs [125] and to improve the locality of loop nests in parallel and sequential code [124]. Although originally presented as a loop transformation technique, the use of data structures to support tiles for generic arrays allows to better exploit the memory hierarchy, since data is often reused within a tile. Tiling can be applied to multiple levels, to distribute work among processors at the outermost level, while locality are enhanced at the innermost level. In the context of distributed-memory, tiles can also make explicit communication, since computations involving elements from different tiles result in data movement [5, 18].

#### 1.1.6 The Trasgo programming framework

Trasgo [43] is a programming framework that is being developed by the Trasgo research group at the University of Valladolid (Spain). Trasgo is based on high-level and nested-parallel specifications allowing easily express several complex combinations of data and parallelism tasks with a common scheme. One of the most important features is that this model hides the layout and scheduling details.

The Trasgo programming system supports its own programming model based on a simple process-algebra model and exploiting data-distribution algebras. Trasgo provides a high level parallel language. The main features of this new language are the following: (1) It is a nested parallel coordination language; (2) it uses extended function interfaces to allow the compiler detect data-flow; and (3), it uses an abstract and unified parallel primitive for coarse- or fine-grain logical tasks. The parallel expressions combine topology and data-distribution plug-in modules to automatically create data-domain partition and mapping.

This high level programming language is translated to an intermediate language called *SPC-XML* to allow the use of powerful XML tools to manipulate it. The framework includes a plug-in system with several modules that generate partition and mapping information, which may be used to create abstract communication codes independently of the mapping details. The framework uses a back-end to translate the internal representation to a parallel source code using the MPI message passing interface as a communication and synchronization layer.

#### 1.1.7 The Hitmap run-time library

Hitmap [45], a runtime library for hierarchical tiling and mapping of arrays, gives support to Trasgo as its back-end. The Hitmap library implements functions to efficiently create, manipulate, map, and communicate hierarchical tiling arrays. Hitmap offers generic mapping functionalities that could be used to implement other tiling arrays solutions (such as HTA) as a special case. The Hitmap topology and layout plug-in system is flexible, extensible, composable at different levels, and supports irregular or load-balancing data partitions with a common interface. These features go beyond HTA functionalities [31, 41]. Hitmap also has a generalized hierarchy system, where a given branch of the hierarchy can be independently and recursively refined, in a dynamic way, to an arbitrary level.

I have participated in the development of Hitmap, and we decided to use it as testbed for our heterogeneous development. In this work we derive a new prototype of Hitmap that includes our proposals to take profit of the computational capability of heterogeneous environments, hiding to the programmer the details about the machine structure and thread management. As we will see, this allows to easily generate programs with multiple levels of parallelism in heterogeneous systems.

#### **1.2** Purpose of this research

#### **1.2.1** Research question

Is it possible to develop a portable and transparent programming system that incorporates hierarchical tiling and scheduling policies, in order to take advantage of heterogeneous computing capabilities?

#### 1.2.2 Tasks

In order to answer to our research question, we have carried out the following tasks:

• We have contributed to the development of Hitmap, a runtime library for hierarchical tiling and mapping of arrays in distributed-memory systems. Starting with the tiling and scheduling framework for distributed-memory systems, we have studied the modifications needed to allow Hitmap to support heterogeneous environments.

- As we will see, this study shows the need for new partitioning levels and their associated policies. This include mechanisms to:

- 1. Transparently move data across devices for GPUs.

- 2. Perform task subdivisions to fit into the devices capabilities.

- 3. Select appropriate shapes and sizes for thread sets.

- The final task is to integrate the proposed mechanisms and policies into an heterogeneous version of Hitmap, evaluating the resulting programming framework with existing benchmarks.

#### 1.2.3 Research methodology

In order to accomplish the objectives proposed in this document, we have followed a research methodology defined by a research method for engineering [2]. This method establishes four phases that the research process has to follow. These phases can be cyclically repeated with the aim of refining the proposed solutions.

- 1. *Observe existing solutions*. This phase has the purpose of detecting the problems that will be addressed during the research process, starting with the existing solutions. It leads to a complete study of the literature, in order to find works related with our research. This study is presented in this dissertation.

- 2. Propose better solutions. In this phase, a solution that overcomes the limitations found in the previous step is proposed. As we will see, there is a lack of frameworks that encapsulate data partition and mapping techniques for heterogeneous environments, automatically and transparently, squeezing the underlying GPU hardware resources. These tasks are closely related to the GPU architecture. We propose several policies to (a) select good values of GPU configurations parameters for some kind of applications, and (b) exploit a good load balancing on an heterogeneous system.

- 3. *Build or develop the solution*. The solution proposed in the previous phase is implemented in this step. We have carried out a study about the GPU architectures and how to help the programmer to determine good values of configuration parameters. We have also developed a prototype programming framework to study the feasibility of the proposed solutions.

#### 1.3. Outline

4. *Measure and analyze the new solution*. Finally, the research method for engineering establishes that the proposed solution has to solve the problems discovered in the first phase. We have evaluated the system using both synthetic benchmarks and some real-world applications.

#### 1.3 Outline

This document is organized as follows. Chapter 2 shows the state of the art through citations and discussions. Chapter 3 presents a runtime library, named Hitmap, whose distributed-memory version will be used to implement new abstractions that support heterogeneous systems composed by CPU and GPU devices. In Chapter 4 we analyze the possibility of creating a programming model to encapsulate the selection of good values of GPU configuration parameters and tile data structures, mapping and load balancing functions, and synchronization/communication functionalities between CPU-GPU heterogeneous devices. As we will see in that chapter, to implement the desired abstraction levels for heterogeneous computing it is needed to arrive to a good data and task partitioning, that it turn leads to the need of an optimal choice of GPU parameters. This issue is covered in Chapter 5. The experimental evaluation of the solutions proposed is carried out in Chapter 6. Finally, Chapter 7, aims to answer our research question, summarizing our results and enumerating the works published during the development of this Ph.D. Thesis. Appendix A shows the fundamentals of the CUDA programming model used to develop the GPU codes, and Appendix B contains some algorithms used as benchmark in our experiments.

# Chapter 2

## State of the Art

This chapter presents the state of the art related to this Ph.D. Thesis. The citations and discussions included in this chapter is the pillar that supports the research work presented in this dissertation.

As we described in the previous chapter, the purpose of this work is to improve programability aspects of heterogeneous systems. Thereby, a broad study of these architectures and their related optimization techniques will be presented. In addition, we will describe tiling arrays supporting tools, that will be the foundation of abstractions to hide the parallel management of data structures in heterogeneous systems. Finally, we discuss the properties and features of some scientific community benchmarks we have selected for our experimental work.

### 2.1 Programming tools for heterogeneous systems

The notion of heterogeneous computing emerged many years ago [17, 76]. This concept is associated with exploiting a system composed by multiple mixed computing devices. We have to highlight the significant growth in the use of the scalable heterogeneous computing system composed by commodity multi-core processors, graphics processors and reconfigurable processors, among others [110]. In these years, heterogeneous computing are gaining more acceptance, while problems, like their energy management, are being gradually solved.

Several programming models can be jointly used to take profit of heterogeneous systems. For example, several works, such as [58, 65] use MPI and CUDA parallel programming models in order to exploit the GPUs devices present in an heterogeneous environment. However, these works do not abstract the use of both models with respect to the target underlying hardware details. Programming using only these tools can be a tedious task.

#### 2.1.1 Programming languages for GPUs

There are multiple global-purpose languages to take profit of GPU capabilities. A first classification criterion is to split them on *Specific* and *General* GPGPU language classes.

A Specific GPGPU language can only be used for a concrete architecture, such as CUDA [61] for NVIDIA platform, and MIC [70] developed by Intel for their architectures. These languages are specifically designed to squeeze the use of the underlying hardware resources. Besides, the programmer has the possibility of using specific code tuning strategies to take even more profit of the target GPU hardware design. On the other hand, a General GPGPU language provides support for multiple vendor devices, such as BrookGPU [19] developed at Stanford University, and the recent OpenCL [60], a standard API for programming both GPGPUs and multi-core CPUs. These general GPU languages do not have specific support to exploit, in the most efficient way, all the GPU hardware resources. Besides, they generally limit the programmer when she wants to optimize a parallel code.

#### 2.1.2 GPU tuning strategies

In our study we are interested in how to transparently reach a high level of efficiency exploiting and taking advantage of the most used GPU architectures, such as those developed by NVIDIA (pre-Fermi, Fermi and Kepler). This goal leads us to choose CUDA as study case for GPGPU languages. There are multiple code tuning strategies in CUDA model [61]. These strategies are currently more complicated to understand and develop than those found on commercial CPUs. Then, to squeeze the computational power of a GPU technology requires much more programming effort.

For example, the work by Wynters [128] shows a naïve matrix multiplication implementation where several threadblock sizes are tested on pre-Fermi architecture. The author says that this configuration has a significant performance impact when a parallel problem is executed on a NVIDIA GPU.

One of most common tuning strategies is to choose a threadblock size that maximizes the SM (Streaming Multiprocessor) Occupancy in order to reduce the memory latencies when accessing the global device memory [61]. The authors focus on block shapes that simplify the programming task, such as square shapes, or dimensions that are power of two (an important part of the search space is not considered).

As [118] states, it is very important to adapt the values of configuration parameters (such as threadblock geometry, shared memory size, and L1 cache memory state) to the particular memory access pattern to squeeze, as far as possible, the computational capability of the heterogeneous systems. Despite the valuable work done in tools, such as FLAME [96] and MCUDA [108], the authors still need to manually determine by trial-

and-error the best values of configuration parameters. The first cite ([96]) focuses on programming dense linear algebra operations on complex platforms, including multi-core processors and hardware accelerators, such as GPUs and Cell. The authors abstract the target accelerator dividing the parallelism in two levels, the first one considering each accelerator device as a computation unit (coarse-grain parallelism), and the second one considering each hardware accelerator as a set of multiple cores (fine-grain parallelism). In the MCUDA paper [108] the authors present a framework to mix CPU and GPU programming. In this work it is mandatory to define separate kernels for all available devices. No data distribution policy is provided, and the toolkit can not make any assumption about the relative performance of the supported devices. Introducing any of these features would involve a redesign of the framework.

There are works, such as [11, 67, 126, 130], that use advanced compilation techniques to transform high-level primitives, or constructors, into optimized CUDA code. However, these frameworks take only into account architectures that are currently deprecated. A simple performance model is introduced in [101], in order to obtain a methodology for predicting execution times of GPU applications in single and multi-GPU environments. However, the citations do not explore the relationships between the threadblock size and shape, and their impact on the hardware resource utilization, which derives in performance impact.

Maximizing the Coalescing factor is another tuning strategy that tries to overlap the communication and computation in order to reduce the latencies in global memory accesses. In [132] the authors show several global memory access strategies in an attempt to reduce these latencies. This work is developed on the pre-Fermi architecture and does not consider global programming parameters, such as L1 cache configurations, threadblock (size or shape) choice.

Other contributions, such as [6, 98], study less common tuning strategies. These works present several problem implementations, testing significant parameters such as unroll factors, prefetching, and work-per-thread among others. The performance obtained by modifying these factors aims to reduce the search space for the optimal configuration. A performance model is also provided. Pre-Fermi is the only considered architecture and the impact of the hardware effects are omitted.

Focusing on more modern architectures (Fermi), in [129] the authors show how the cache memory hierarchy helps to take advantage of data locality, thus, significantly improving the global performance. However, taking into account the cache hierarchy leads to a too much complicated performance prediction model. The authors study a particular benchmark where the shared-memory vs. transparent cache configuration is adjusted automatically depending on the amount of data assigned to threads. Again, the effects of the block size and shape are not considered. Finally, in [36, 59], for the same GPU architecture, the authors show several interesting metrics related to hardware architecture.

The authors use these metrics in an attempt to predict the performance of CUDA kernel codes once the block shape is manually chosen.

## 2.2 Challenges in heterogeneous programming

#### 2.2.1 Data partition and load balancing techniques

Load-balancing methods for heterogeneous systems try to distribute the workload among computing units according to their computational capabilities. There are several loadbalancing methods suitable not only for traditional systems, but also for heterogeneous systems. In the rest of this section a brief discussion of these methods is shown.

The use of some heuristics or data partition policies can be very useful to improve the load balancing in any environment. Some works, such as [54, 131], exploit at the same time CPU and GPU devices, attempting to obtain a good load balance. However, data-structures partition and manipulation is not abstracted and authors do not support flexible mechanisms to add new partition and layout policies.

Chapel [27], proposes a transparent plug-in system for domain partitions in generic systems. It tries to hide the communication issues to the programmer. Most of the times efficient aggregated communications can not be automatically derived from generic codes. Moreover, the authors do not offer specific support for accelerator partition policies, or synchronization among different CPU and GPU devices. The authors in [66] create a model to estimate the execution time of each task (based on the number of instructions and input data size), thus deciding which hardware would be the best for each case. The size of each single task is fixed at compilation time. In [66, 100] the authors calculate the data transfer time between the different devices (GPUs and CPUs), and also create a model in order to reduce inter-GPU and CPU-GPU communication.

Other authors [56, 122] try to assign bigger data portions to the most powerful devices. However, the data portion size has to be initially fixed. On the other hand, in [32], all tasks have the same size, and the number of tasks assigned to each hardware depends on the computing capacity of each device.

Graph dependencies are commonly used to discriminate which data-portion or area are more profitable for each target architecture. An input data-portion represents the minimum data unit scheduled on the heterogeneous hardware devices. This technique is used to represent any kind of dependencies between the different input data-portions, improving the load-balance factor in heterogeneous environments [20, 26, 34]. Nevertheless, the recovery of the necessary information to fill the graph can be time consuming. Works like [34] and [26] describe how to create a complete dependence-graph in order to classify as dependent or independent the application tasks. Only independent tasks are launched to GPU devices in order to reduce the costly data transfers through inter-GPU communications. In [20], the authors make a study of DDAs (data dependencies algebras) and use this technique to improve the load-balance between a cluster of GPUs minimizing the memory bottlenecks.

Finally, there are training methods to estimate the most costly computation portions, and select an appropriate device to execute them. These methods select a small subset of input data and execute the related part of the computation in the target system. The execution is monitored and performance results registered. The information is then used to predict the global execution time, which are the most powerful devices, or even which devices are more appropriate for each input data-portion.

#### 2.2.2 Memory size restrictions

Taking into account the memory size limitations of heterogeneous target devices is an additional challenge. Currently, many approaches do not focus in this problem, working with fixed sized middle-grain tasks [32], or assuming that the tasks fit, or are generated to fit into the devices [14, 20]. Other approaches simply advise to add more computation devices to allow finer partitions [10]. A simple way to tackle the problem is to generate more distributed processes than system nodes, mapping several of them to the same device [115]. In this way, each process is responsible for a smaller part of the computation. When enough processes are launched, the parts are small enough to fit in any target device. However, this leads to more costly inter-process communications and scalability problems. A more sophisticated approach is to consider the device memory limitations while creating the high-level partition [12]. This approach highly complicates the whole partitioning activity.

An associated problem for memory-restrictions-aware systems is to find a proper representation of the parallel computation that allows the system to locate, and measure the size, of the data portions required by a generic part of the computation. This information is needed for both generating a balanced partition, and mapping the parts adequately, even for libraries that make transparent the node to device communication (e.g. [3, 12]).

None of these works propose a solution to allow a hidden layer to split an arbitrarily large computation in parts that fit the memory limitations of an assigned target device, or to transparently launch the partial computations generated to the target devices.

#### 2.2.3 Tiling support

We have already discussed tiling techniques in Sec. 1.1.5. There is a lack of tiling support in most programming languages, with the exception of some data-parallel languages such as HPF [69] and PGAS languages (e.g. UPC [22]). Both supply some constructors to align and distribute data among processors. HPF offers a limited set of patterns computed at compile time. Moreover, HPF does not offer a truly composable distribution mechanism, since it is not possible to apply a second data distribution over the local part of a previous distribution. For example, block-cyclic distributions can not be programmed as a composition of cyclic over block distribution.

Regarding PGAS languages, it is responsibility of the programmer to define and distribute tiles, frequently in terms of the number of processors or specific architecture details. This leads to the development of code that is hard to read and maintain. Finally, HTA [13, 49] is an elegant implementation of hierarchically tiling arrays in objectoriented languages as an abstract data type. However, this implementation does not supports irregular or load-balancing data partitions with a common interface.

### 2.3 Benchmarking

#### 2.3.1 Micro-Benchmarking for GPUs

The use of micro-benchmarks to evaluate hardware configurations has a long tradition. There is not too much related work in the scientific community about the use of these benchmarks to understand the GPU hardware behavior. The GPU devices present significant performance changes when both, the problem implementation, and the values of configuration parameters (such as threadblock size-shape or, L1 cache state) are even slightly modified. In the rest of this section several approaches to micro-benchmarking techniques are discussed.

A set of micro-benchmarks is described in [109] in order to obtain measures related to architectural features, and basic program characteristics. These features and characteristics include vectorization, burst write latency, texture fetch latency, global read and write latency, ALU/Fetch operation. However, the study only focuses on the AMD GPU architecture.

The authors in [127] introduce a suite of micro-benchmarks to measure the performance of GPUs as well as the performance impact when a specific optimization strategy is used. The authors measure execution times and obtain the different latencies for the same threadblock configuration. In [4], the authors try to find the lower and upper bounds of the partition camping problem [47]. They present performance results related to the global memory read and write operations, with and without partition camping. As a result, the authors provide a spreadsheet that calculates an estimation of the partition camping problem for a given kernel. The authors do not consider the full range of threadblock size and shape choices. All these studies are only focuses on the first NVIDIA released architectures.

Several authors like [55, 133] have tried to develop performance analytic models that help the user squeezing the GPU computational capabilities. In [133], the model is based

#### 2.3. Benchmarking

on the results of a set of micro-benchmarks in order to measure the time of each kind of instruction, and the global/shared memory accesses. The authors always use the same threadblock shapes (square geometry) and extrapolate the memory data transfer bandwidth. In [55], the authors identify two main parameters related to the efficiency of the hardware resources use: (1) The time that a warp is waiting for data, and (2) the number of operations that could be done during these delays. The authors estimate the values by a set of micro-benchmarks. Again, different threadblock shapes have not been considered.

In summary, all these works do not systematically explore all the threadblock configuration space. Moreover, several of these tests have been conducted using deprecated GPU architectures, and do not relate the threadblock configuration with the underlying hardware effects.

#### 2.3.2 Choice of benchmarks used in this work

This section briefly discusses the most relevant benchmarks used throughout this Ph.D. Thesis. A more complete description of the different benchmarks is included in Appendix B at the end of this document.

The desirable properties of benchmarks to test the different tuning strategies studied on this work are the following: (1) benchmarks should have data reutilization and different memory access pattern for each input data structure; (2) specific benchmarks should be designed to exploit distributed memory systems where each one is composed by devices of different nature; and (3), real-world benchmarks characterized as embarrassing parallel applications to avoid the communication overhead, where each individual input datum can be processed independently, are desirable. This set of benchmarks covers the most common kernel features for GPU implementation codes. Therefore, we will use them as relevant benchmarks to test the GPU hardware effects under the influence of its configuration parameters.

First, we will consider simple linear algebra kernels that represent typical coalesced access patterns. A good example of these benchmarks, is the matrix-matrix multiplication where the simplicity of the algorithm helps to better understand the GPUs behavior. One matrix-matrix multiplication variant (Cannon's algorithm [21]) is also used, whose main feature is to exploit distributed-memory systems. This method distributes data portions among all available hardware accelerators.

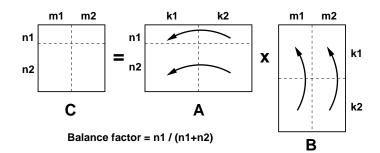

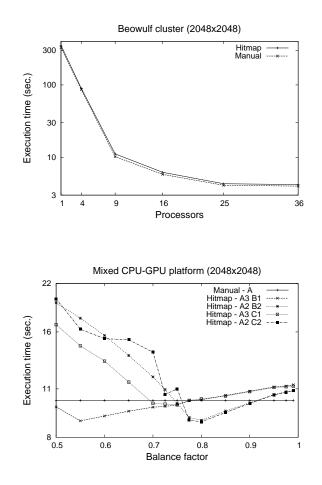

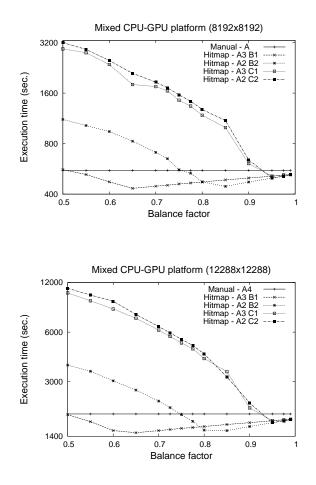

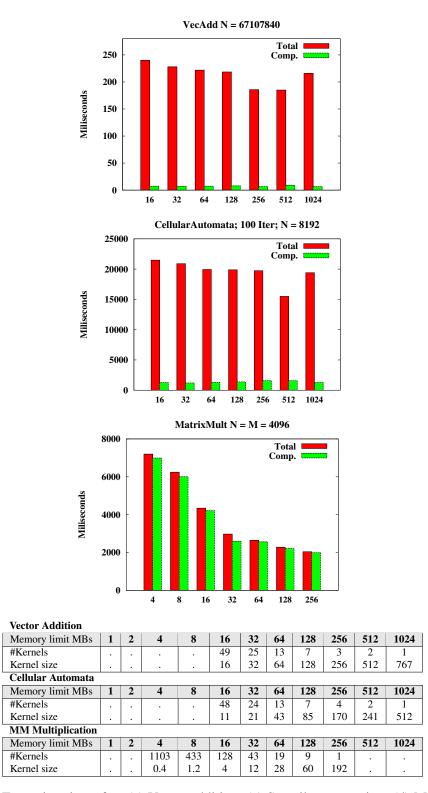

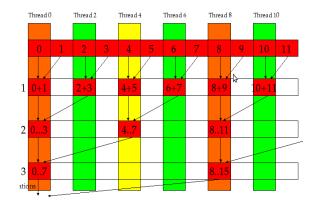

Second, we will use real-world applications. These benchmarks are characterized by being more complicated than the previous ones since they are composed by more than one kernel with very different features. The first real-world benchmark that we will use is the Single-Source Shortest Path (SSSP) problem, a classical problem of optimization. Many problems that arise in real-world networks imply the computation of the shortest path and its distances from a source to one or more destination points. Some examples